# 倾听 JESD204B：一种适用于基于 FPGA 的超声采集系统的轻量级开源 JESD204B IP 内核

Soumyo Bhattacharjee\*, Federico Villani\*, Christian Vogt\*, Andrea Cossettini\*, Luca Benini\*

Email: sbhattacharj@student.ethz.ch, villanif@ethz.ch

\*Department of Information Technology and Electrical Engineering, ETH Zurich, Switzerland

**摘要**—超声系统对数百个紧密同步的通道以每秒数十兆样本的速度运行的需求超过了传统低压差分信号链路的带宽、引脚数量和延迟。尽管 JESD204B 串行接口缓解了这些限制，但商用 FPGA IP 核心是专有的、昂贵且资源密集型的。我们提出了 ListenToJESD204B，这是一个在 AMD Xilinx Zynq UltraScale+ 设备上以宽松的 Solderpad 0.51 许可发布的开源接收 IP 内核。该内核采用可综合 SystemVerilog 编写，支持四个 GTH/GTY 通道，速率可达 12.8 Gb/s，并提供精确到时钟周期的 AXI-Stream 数据以及确定性的子类 1 延迟。它仅占用 107 个可配置逻辑块（大约 437 个查找表），相比同类商用 IP 减少了 79%。模块化的数据路径包括每通道弹性缓冲器、SYSREF 锁定的 LMFC 生成和可选 LFSR 解扰，便于扩展到高通道数量。我们通过与 Xilinx JESD204C IP（在 JESD204B 模式下）的仿真对比以及使用 TI AFE58JD48 ADCs 的实际硬件验证了协议的一致性。通过流传输每秒 80 兆样本、16 位采样，持续 30 分钟无错误，我们验证了块状稳定性。

**Index Terms**—JESD204B 子类 1, 开源硬件, FPGA 集成

## I. 介绍

基于 FPGA 的超声系统为关键医疗应用提供了灵活、实时的诊断成像，包括紧急现场护理场景、可穿戴健康监测和快速床边诊断，促进即时临床决策并改善患者预后 [1]。高速数据采集对于这些成像技术至关重要，需要从模拟前端 (AFE) 设备到数字处理单元之间进行高效且可靠的数据传输 [2]。随着成像系统朝着更高通道数、更高速采样率和紧凑外形发展，传统接口如低压差分信号 (LVDS) 由于有限的可扩展性、高引脚数量以

The authors acknowledge support from the ETH Research Grant ETH-C-01-21-2 (Project ListenToLight).

及在高速数据率下的信号完整性问题变得受限 [3], [4]。这种限制尤其阻碍了新兴便携式生物医学系统的发展，例如 TinyProbe [5] 和可穿戴成像平台 [6]，它们依赖于具有有限输入输出 (IO) 接口的紧凑型 FPGA。

JESD204B 标准提供了一个可扩展的、标准化的替代方案，减少了接口复杂性并确保了确定性的延迟，这对于准确的实时成像和波束形成至关重要。现有的商业 IP 解决方案，如 Xilinx LogiCORE JESD204 IP (v5.2)，已经成熟，但受到限制性许可模型、有限透明度和高昂成本的影响，这限制了它们在开放研究和模块化平台开发中的适用性。此外，这些商用解决方案需要支持大量的替代配置，因此，在希望实现最小化且轻量级的实施时（例如用于可穿戴系统），会导致 FPGA 资源利用率不佳。因此，尽管与 LVDS 相比有明显优势，现有的 JESD204B 解决方案和开源采用仍受到这些瓶颈的限制。

为了解决这一差距，我们提出了监听 JESD204B，这是一个完全开源的、资源高效的 JESD204B 子类 1 接收专用 IP 核心，采用可综合的 SystemVerilog 编写。它针对 AMD Zynq UltraScale+ ZU19EG MPSoC，并实现了完整的 JESD204B 子类 1 接收规范，支持每个通道高达 12.8 Gbps 的四个通道。

我们的关键贡献是：

- **开源子类 1 RX IP:** 一个公开可用的 SystemVerilog 核心，实现了 JESD204B 接收堆栈的最大标准比特率。

- **资源高效的架构:** 相较于领先的商业 IP，展示了在查找表 (LUT) 和触发器 (FF) 利用率上减少了 79%，这一结果通过 ZU19EG MPSoC 的仿真和硅验证得到了证实。

- **高速超声捕获：**演示通过模拟前端在两个 12.8 Gbps JESD204B 通道上可靠获取 80 MSPs 模拟信号。

## II. 背景及相关工作

FPGA 基础架构由于其内在的并行性、确定性的时序和可重构性，在生物医学超声成像中被广泛使用。早期使用 LVDS 的 FPGA 实现仅适用于适度的通道数量 [7]。Boni 等人提出的开放式平台 [2] 强调快速开发和实验，但受限于 LVDS 的限制，在高通道数场景中影响了可扩展性和同步性。

如 Risser 等人 [8] 的 1024 通道体积超声平台进一步说明了管理多 FPGA 设置的复杂性，因为传统与 AFE 接口的方法需要随着不断增长的通道数量而具有非常高的引脚数。

自 JEDEC [9] 引入以来，JESD204B 由于其可扩展性和确定性延迟而成为高速 ADC 接口的首选。然而，由于依赖于专有 IP 内核，它在开源社区中的广泛采用仍然有限，正如王等人 [10] 所说明的那样。即使某些实现使用了 JESD204B 标准，设计的源代码也没有公开提供 [11]。

当前开源的 JESD204B 解决方案如 Analog Devices 的 HDL 框架 [12] 和 LiteJESD204B [13] 是重要的参考，但仍存在一些问题。前者实现没有使用宽松许可证，并且需要修改才能使设计在 AMD Xilinx Ultrascale+ 平台上与不同供应商的 AFE 正确运行，而后的开发基于 Migen [14]，这是一个尚未被广泛采用的工具链，仅验证了高达 6.25 Gbps 的数据速率，并不支持未加密模式。

*ListenToJESD204B* 通过提供一个紧凑、易于集成和扩展以及完全开源的 IP 核来解决关键差距。. Supporting AMD Xilinx JESD204 Physical layer (PHY) block compatibility, deterministic Subclass 1 latency, and robust infrastructure, it bridges the gap toward scalable, reproducible, and community-driven biomedical ultrasound system design research.

## III. 系统上下文

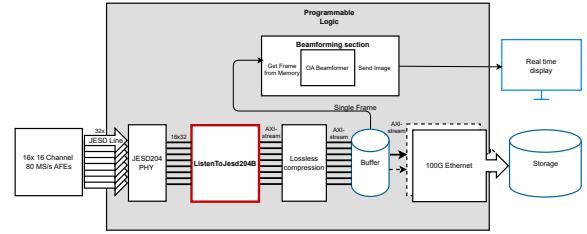

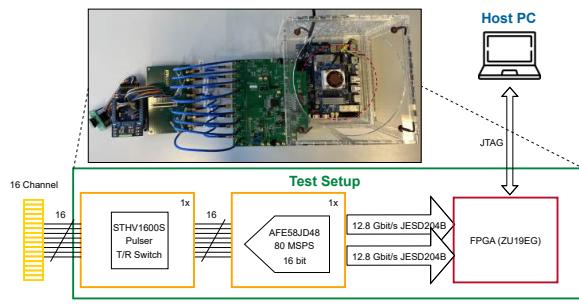

图 1 说明了将监听 JESD204B 接收器集成到一个紧凑、高性能的开放式超声前端架构中，该架构针对最先进的成像进行了优化。十六个 TI AFE58JD48 模拟前端每个以每秒 80 兆样本和 16 位分辨率对 16 通道

图 1. 256 通道开放式超声前端的框图。监听 JESD204B 核心将 32 个 JESD204B 通道转换为并行数据，然后进行无损压缩和存储，并且为了实时成像而重建。

进行数字化处理，产生大约 327Gb/s 的数据量，跨越 256 个通道。每个 AFE 通过双通道 JESD204B 接口流式传输数据，导致有 32 条高速通道直接与 AMD Xilinx ZU19EG 系统级芯片 (SoC) 的 GTH 收发器对接。供应商提供的 JESD204 物理层与开源监听 JESD204B 接收器结合，执行解串行化和字对齐操作，向 FPGA 结构提供一个 256 位并行流。

由于在这些数据速率下 DRAM 存储不切实际，数据流会立即进行实时压缩 [15]。超声回波数据通常能实现 4 到 6 的压缩因子，将所需的外发带宽降低至约 70Gb/s。这可以舒适地适应一个支持 RDMA 的 100 Gb 以太网链路 [16]，从而能够直接转发到 GPU 集群或本地 NVMe 归档。数据路径的紧凑架构允许在 FPGA 结构中集成一个可重构模块，该模块可以执行实时成像和波束成形 [17]，使获得的数据能立即可视化。

#### IV. 架构与实现

监听 JESD204BRx IP 实现了一个模块化、简单且可综合的 SystemVerilog 设计，用于 FPGA 平台上的 JESD204B 子类 1 接口。其架构由通过标准化流接口连接的特定协议子模块组成，便于重复使用、独立验证以及集成到更广泛的数据采集管道中。

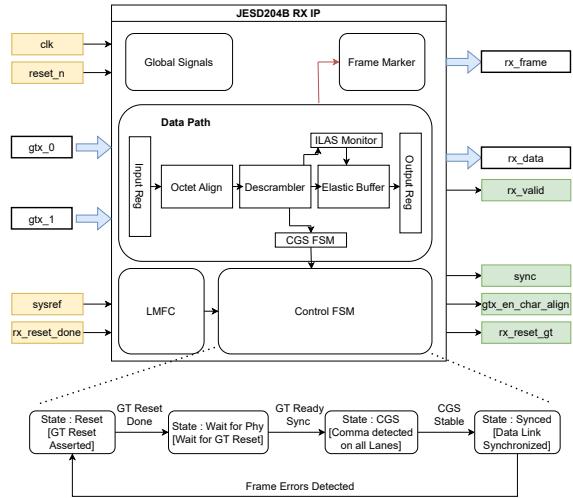

图 2. JESD204B 接收器的高层架构

设计用于与 Xilinx 的 JESD204 PHY 使用 GTY/GTH 收发器进行接口，该 IP 支持最多四条通道和从 6 Gbps 到 12.8 Gbps 的线路速率。它输出符合 AXI-Stream 的数据，简化了下游连接。为了使 IP 易于用户使用，每个链路的最大通道数设置为 4 个，但可以在封装级别轻松修改。所有底层模块都兼容每链路最多 32 条通道。图 2 说明了 JESD204B 接收器的高层架构，表 I 列出了 IP 可配置参数。

表 I

接收器 IP 的可配置参数

| 参数   | 描述                                 | 范围      |

|------|------------------------------------|---------|

| 链接 L | Number of JESD204B links supported | up to 4 |

| F    | Number of lanes per link           | up to 4 |

| K    | Octets per frame                   | 4 - 32  |

| 解扰码  | Frames per multiframe              | 1 - 32  |

| 数据宽度 | Enable flag for data descrambling  | 0 / 1   |

|      | Width of the datapath (in bits)    | 32 bits |

##### A. 数据路径

每个 JESD204B 通道连接到一个专用的数据路径模块，负责每周期处理四个 8 位八进制数。这些模块注

册输入数据，执行代码组同步 (CGS)，验证初始通道对齐序列 (ILAS)，执行可选的去扰码，并使用每个通道的弹性缓冲区对齐数据。通过将 CGS 和 ILAS 逻辑封装在数据路径内，架构避免了控制与数据移动之间的耦合，保持了清晰的数据流语义。

顶层接收器聚合车道输出并发出与 AXI-Stream 兼容的数据，并带有 rx\_ 有效信号。核心假设下游系统连续消耗数据，不支持通过准备就绪进行反压。GT 配置（包括 PLL 锁定和 8b/10b 解码）预计由外部管理，尽管提供了挂钩以实现更紧密的集成。

##### B. 控制状态机

有限状态机 (FSM) 在五个主要状态下协调链路初始化：重置，ST\_ 等待\_ 物理，ST\_CGS，ST\_ILAS 和 ST\_ 同步。在 ST\_CGS 中，FSM 监控逗号对齐的/K28.5/字符，并断言 JESD204B 的同步信号以提示发射机对齐。检测到一致的 CGS 后，FSM 进入 ILAS 验证阶段，检查所有多帧的有效配置字段。一旦确认通道对齐，系统将过渡到数据接收。

一个稳定标志和循环计数器门状态转换以防止由于瞬态而过早推进。具有可配置阈值的故障检测逻辑确保在出现不对准时重新进入 CGS。

##### C. 八位对齐和解扰

来自收发器的 10 位符号首先使用八位对齐模块进行解码和字节对齐，该模块检测/K28.5/字符并相应地旋转输入单词。这确保了后续 ILAS 和数据八位字节的正确帧定位。去扰操作使用流水线式 32 位宽的基于线性反馈移位寄存器 (LFSR) 的模块来实现  $G(x) = x^{14} + x^{13} + 1$ 。这两个功能每条通道独立运行，并可通过 RTL 参数进行配置。

##### D. SYSREF-同步 LMFC 生成

为了强制确定性延迟，接收器包含一个与 SYSREF 同步的 LMFC 生成器。计数器在 SYSREF 边沿复位，并且每  $F \times K$  个八位组循环一次，建立可重复的多帧边界。这个同步的 LMFC 用于控制跨通道的弹性缓冲释放。

##### E. 弹性缓冲区

每车道的弹性缓冲区作为环形 FIFO 实现，补偿偏斜并将数据对齐到 LMFC 边界。一个中央缓冲释放模

块监测所有缓冲区的状态并触发同时的数据释放。缓冲深度是静态可配置的，以适应特定应用的偏斜容差。

#### F. 设计考虑因素

该IP是在考虑可移植性和集成性的前提下开发的。关键设计选择包括：

- 统一时钟：**所有内部逻辑均由单一时钟驱动，以避免时钟域交叉（CDC）问题。

- 固定数据宽度：**32位宽处理与收发器输出和AXI-Stream期望一致。

- 紧凑控制逻辑：**FSMs是浅层的，并针对320MHz的时序闭合进行了优化。

- 模块化布局：**数据路径、控制和同步的清晰分离有助于可测试性。

- Vivado IP 包装器集成：**图形用户界面配置和模块设计兼容性支持易于采用。

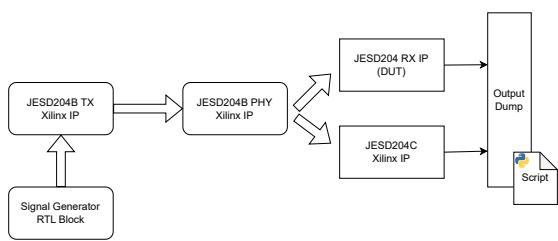

图 3. 基于仿真的 JESD204B 接收器 IP 核验证设置。测试平台使用黄金输出来评估实现设计的功能正确性。

## V. 验证方法与结果

一个两阶段的方法被用来评估监听 JESD204B 接收器的功能正确性和实际集成：行为仿真和硬件回路测试。这确认了协议合规性，子类 1 确定性行为，以及与实时数据采集系统的兼容性。

#### A. 基于仿真的验证

初始验证是在 Xilinx 的 JESD204C 示例设计派生的仿真环境中进行的。测试平台（见图 3）进行了修改，以插入接收器 IP 作为待测设备（DUT），并配置为使用 Xilinx JESD204C IP 在 B 模式下模拟 JESD204B 发射机。每帧的字节和每个超帧的帧数在两个模块之间匹配，以确保一致性。

仿真在 Vivado 2023.2 中执行。测试向量包括 CGS、ILAS 和随机负载，以验证典型和边界情况流量模式的处理。接收器输出与配置相同的参考实现进行了比较。

断言验证了 FSM 状态的正确转换、ILAS 提取和多帧对齐。

#### B. 硬件评估设置

为了验证实时性能，所提出的接收器 IP 被部署在 Xilinx Zynq UltraScale+ MPSoC (ZU19EG) 上，作为超快速超声采集平台的一部分（如图 6 所示），该平台配有一个 5MHz 32 通道超声换能器 (Vermon)，其中 16 个通道连接到一个 16 通道的 STHV1600 超声脉冲发生器 (STMicroelectronics)，一个 16 通道、80 MSamples/s AFE58JD48 模拟前端 (AFE) (Texas Instruments)，并通过 2 JESD 链路，以每秒 12.8G 样本的速度传输到 ZU19EG FPGA。用于子类 1 同步和时钟的 SYSREF 信号由 LMK04826B 时钟调节器 (Texas Instruments) 提供。通过集成逻辑分析仪缓冲区捕获 JESD204B 核心接收到的数据，并通过 JTAG 传输到主机 PC。此外，使用 ILA 监控内部信号，包括 LMFC 时钟、FSM 状态和数据对齐标志。为了测试长期稳定性，实验运行了三十分钟。在此期间，未观察到无效帧。该配置在实际操作条件下评估采集稳定性和链路同步以及协议合规性，略高于 JESD204B 规范的 12.5Gbps 限制。

多次实验验证了与真实数据转换器和外部信号源的集成。在第一次测试中，ADC 以 80 MSPS 的速度通过 16 个通道传输了一个数字斜坡模式，并将其交织到两个运行速度为 12.8 Gbps 的通道中。接收核心成功地对齐了 8B/10B 编码流，执行了解扰，并将重构后的样本转发到了高速缓冲区进行分析（未显示）。通道同步在初始化后 15 个帧时钟周期内完成。

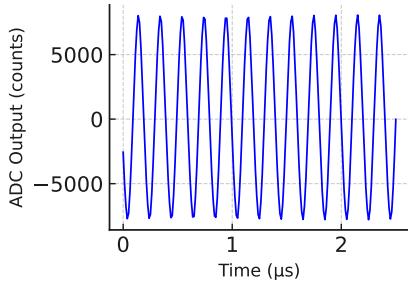

在第二次测试中，将信号发生器产生的精度为 5 MHz 的正弦波（峰峰值 0.6V，偏移量 0V）连接到 AFE58JD48 输入通道。接收器能够在扰码和解扰模式下准确重构波形。图 4 显示了重构后的信号。

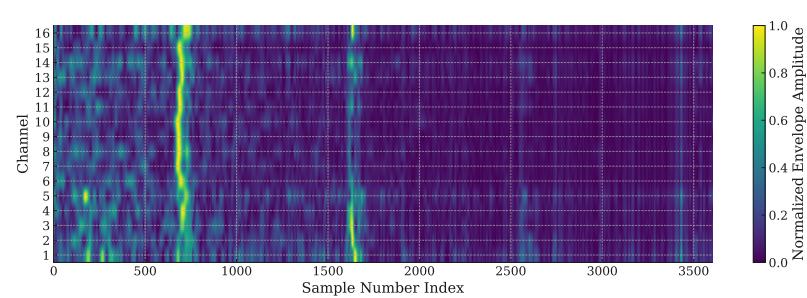

第三次测试使用了 Cirs 040GSE (Sun Nuclear) 组织模拟体模。采集超声换能器被定位以成像体模的垂直距离散射体（等间距反射器，间隔为 1.5 厘米）。换能器用 3 周期、5 MHz、20VPP 平面波 0 脉冲激发以生成超声信号。接收器在所有 16 个通道上以 80 MSPS 的速度捕获了 8000 个样本，随后进行了带通滤波（1-10 MHz）、使用希尔伯特变换进行包络检波，并进行了窗口化处理。图 5 展示了所得的原始信道数据，显示了等

图 4. 使用 JESD204 接收 IP 获取和重建 5 兆赫正弦波

图 5. 获得 CIRS 040GSE 超声仿体中的散射体

图 6. 用于验证 JESD204B 接收核心的实验测试设置

间距的四个不同反射器，并验证了一个现实的端到端超声采集管道的设计。

### C. 定时和资源利用

接收器使用 Vivado 2023.2 进行综合，针对 Zynq UltraScale+ ZU19EG 设备。核心在 320 MHz 的时钟速率下满足了定时要求 (JEDEC JESD204B 标准支持的最大时钟)，最差负松弛时间为 0.31 ns。

表 II

资源利用率比较对于两通道实现

| 资源            | 这项工作 |      | Xilinx IP<br>JESD204C |

|---------------|------|------|-----------------------|

|               | 解扰码  | 解扰离散 |                       |

| CLB LUTs      | 437  | 426  | 2092                  |

| CLB Registers | 429  | 410  | 1988                  |

| CARRY8 Blocks | 2    | 2    | 46                    |

| F7&F8 Muxes   | 0    | 0    | 96                    |

| CLBs          | 107  | 102  | 470                   |

表 II 报告了我们解决方案的资源利用率。实现相较于 Xilinx IP 达到了显著的逻辑节省 (我们的实现仅使用了 21% 的查找表和寄存器，相比之下 Xilinx IP 使用更多)，同时保持协议合规性和子类 1 确定性。Xilinx

IP 另外提供了通过 AXI 接口进行运行时配置的更高可重构性。排除这些额外特性为计算密集型处理块留出了更多的空间。通过最小化接收接口的占用，我们的设计使得支持更多采集通道成为可能，同时为下游处理保留足够的 FPGA 容量。

在第一个有效样本出现之前观察到一个固定的启动延迟，为 13 个时钟周期 (40 纳秒)，之后吞吐量与 Xilinx JESD204C IP 匹配。

## VI. 结论

本文介绍了监听 JESD204B，一个紧凑且完全开源的接收器 (Rx) IP 核，它以模块化和资源高效的方式实现了 JESD204B 子类 1 协议。该内核使用可综合 SystemVerilog 设计 (通过 Vivado IP Packager 封装)，并在 Xilinx UltraScale+ FPGA 上进行了测试，支持最多 4 路通道配置及 12.8 Gbps，并能够干净地集成到开源硬件平台中。功能验证是通过仿真和环路硬件测试完成的，展示了协议符合性和稳定的时间行为。该设计实现了 79% 更低逻辑利用率的时间收敛，相比领先的商业 IP，使其适用于需要确定性高速串行接收的嵌入式 FPGA 系统。

可能的扩展工作包括支持 Subclass-0 和 Subclass-2 模式，并开发一个互补的发射机 IP 核以实现完整的链路验证。另一个重要的补充是一个模块化、可重用的测试平台框架，以便系统地验证当前接收机核心及未来扩展。

## VII. 数据可用性

开源监听 JESD204BRX IP 核在宽松的 Solderpad 0.51 许可证下发布，并公开可用：[github.com/pulp-bio/JESD](https://github.com/pulp-bio/JESD)

## 参考文献

- [1] M. W. Schellenberg and H. K. Hunt, "Hand-held optoacoustic imaging: A review," *Photoacoustics*, vol. 11, pp. 14–27, Sep. 2018.

- [2] E. Boni, A. C. H. Yu, S. Freear, J. A. Jensen, and P. Tortoli, "Ultrasound Open Platforms for Next-Generation Imaging Technique Development," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 65, no. 7, pp. 1078–1092, Jul. 2018.

- [3] E. Boni, L. Bassi, A. Dallai, F. Guidi, V. Meacci, A. Ramalli, S. Ricci, and P. Tortoli, "ULA-OP 256: A 256-Channel Open Scanner for Development and Real-Time Implementation of New Ultrasound Methods," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 63, no. 10, pp. 1488–1495, Oct. 2016.

- [4] J. A. Jensen, H. Holten-Lund, R. T. Nilsson, M. Hansen, U. D. Larsen, R. P. Domsten, B. G. Tomov, M. B. Stuart, S. I. Nikolov, M. J. Pihl, Y. Du, J. H. Rasmussen, and M. F. Rasmussen, "SARUS: A synthetic aperture real-time ultrasound system," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 60, no. 9, pp. 1838–1852, Sep. 2013.

- [5] S. Vostrikov, J. Tille, L. Benini, and A. Cossettini, "TinyProbe: A Wearable 32-Channel Multimodal Wireless Ultrasound Probe," *IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 72, no. 1, pp. 64–76, Jan. 2025.

- [6] D. Speicher, T. Grün, S. Weber, H. Hewener, S. Klesy, S. Rumanus, H. Strohm, O. Stamm, L. Perotti, S. H. Tretbar, and M. Fournelle, "Wearable 256-Element MUX-Based Linear Array Transducer for Monitoring of Deep Abdominal Muscles," *Applied Sciences*, vol. 15, no. 7, p. 3600, Mar. 2025.

- [7] Gi-Duck Kim, C. Yoon, Sang-Bum Kye, Y. Lee, J. Kang, Y. Yoo, and Tai-kyong Song, "A single FPGA-based portable ultrasound imaging system for point-of-care applications," *IEEE Transactions on Ultrasonics, Ferroelectrics and Frequency Control*, vol. 59, no. 7, pp. 1386–1394, Jul. 2012.

- [8] C. Risser, H. Hewener, M. Fournelle, H. Fonfara, S. Barry-Hummel, S. Weber, D. Speicher, and S. Tretbar, "Real-Time Volumetric Ultrasound Research Platform with 1024 Parallel Transmit and Receive Channels," *Applied Sciences*, vol. 11, no. 13, p. 5795, Jun. 2021.

- [9] JEDEC, "JESD204B: Serial Interface for Data Converters," <https://www.jedec.org/sites/default/files/docs/JESD204B.pdf>, Jul. 2011.

- [10] R. Wang, J. Zhang, C. Jiang, and H. Liu, "High-Speed ADC Interface Design Based on JESD204B Protocol," in *SPIE Smart Photonic and Electronic Microsystems Conference (SPCS)*, 2023.

- [11] C. González, M. Ruiz, A. Carpeño, A. Piñas, D. Cano-Ott, J. Plaza, T. Martínez, and D. Villamarín, "Hardware Acceleration of Digital Pulse Shape Analysis Using FPGAs," *Sensors*, vol. 24, no. 9, p. 2724, Apr. 2024.

- [12] Analog Devices, "JESD204 Interface HDL Framework," <https://github.com/analogdevicesinc/hdl/tree/main/library/jesd204>.

- [13] enjoy-digital, "LiteJESD204B: Open-Source JESD204B IP Core," <https://github.com/enjoy-digital/litejesd204b>, Apr. 2025.

- [14] m-labs, "Migen," <https://github.com/m-labs/migen>, May 2025.

- [15] F. Villani, S. Mathys, Ç. Özsoy, X. L. Deán-Ben, A. Cossettini, M. Magno, D. Razansky, and L. Benini, "FPGA-Accelerated Hybrid Lossless and Lossy Compression for Next-Generation Portable Optoacoustic Platforms," in *2024 IEEE Ultrasonics, Ferroelectrics, and Frequency Control Joint Symposium (UFFC-JS)*, Sep. 2024, pp. 1–5.

- [16] A. Cossettini, K. Taranov, C. Vogt, M. Magno, T. Hoefer, and L. Benini, "A RDMA Interface for Ultra-Fast Ultrasound Data-Streaming over an Optical Link," in *2022 Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Mar. 2022, pp. 80–83.

- [17] F. Villani, Ç. Özsoy, C. Vogt, A. Cossettini, X. L. Deán-Ben, M. Magno, D. Razansky, and L. Benini, "Adaptive Image Reconstruction for Optoacoustic Tomography: A Partial FPGA Reconfiguration Approach," *IEEE Sensors Letters*, vol. 8, no. 8, pp. 1–4, Aug. 2024.